在现代电子工程设计领域,高速电路设计无疑是一个至关重要且复杂的课题。随着科技的飞速发展,电子设备对速度和效率的要求越来越高,这使得高速电路设计成为电子工程师必须掌握的基本技能。本文将深入探讨高速电路设计的核心要素,以帮助工程师们在实际应用中实现高效、稳定的电路设计。

一、理解基本概念与理论

1、信号完整性

信号完整性是指信号在传输过程中保持其原有特征和形状的能力。它主要关注信号的时序、噪声和电磁干扰等方面。信号完整性问题通常是由传输路径上的信号反射、串扰等因素引起的。在高速电路设计中,信号上升沿或下降沿的变化速度极快,这会导致高次谐波分量的增加,从而引发更多的信号完整性问题。因此,控制信号的上升时间和带宽是关键。

2、阻抗匹配

阻抗匹配是确保信号在传输线上无反射地从源端传递到负载端的重要手段。不匹配的阻抗会导致信号反射,进而引起振铃和信号失真。在高速电路设计中,通常通过控制传输线的特性阻抗(如50欧姆或75欧姆)来实现阻抗匹配,从而减少信号的反射。

二、设计策略与技术要点

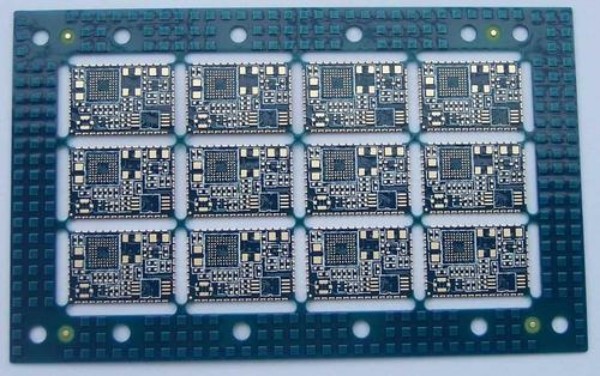

1、多层板的应用

多层板是高速电路设计中不可或缺的一部分,它能有效降低电路干扰,提高信号传输可靠性。通过合理选择层数和设置内部电源层及接地层,可以显著减少寄生电感和信号间的交叉干扰。布线时应避免相邻两层的走线方向相同,以防互相干扰。

2、合理的布局与布线

在PCB设计过程中,应尽量缩短高速电路器件管脚之间的引线,以减少分布电感和分布电容的影响。同时,各个高速电路器件管脚间的引线层间交替越少越好,即过孔数目应尽量少,因为每个过孔都会带来约0.5pF的分布电容,增加信号延时。此外,布线时应避免形成环路,并尽量减少平行布线的長度,以防止“交叉”干扰。

3、去耦电容的配置

去耦电容在高速电路设计中扮演着重要角色。它们能有效地抑制高频噪声和干扰信号,提高电路的稳定性和可靠性。设计时,应在集成电路块附近设置一个或多个高频去耦电容,以滤除供电回路中的高频噪声。同时,去耦电容的选型和位置也非常关键,需要根据具体电路情况来确定。

三、实践技巧与案例分析

1、仿真软件的使用

熟练使用各种仿真软件是高速电路设计的必备技能。这些工具可以帮助工程师在实际制作电路板之前,对设计方案进行验证和优化。通过仿真分析,可以及时发现潜在的问题并进行调整,从而提高设计的准确性和可靠性。

2、实测与校准

除了理论分析和仿真验证外,实际测试也是高速电路设计中不可或缺的一环。通过测量设备对设计好的电路进行测试,可以得到真实的性能数据,进而对设计方案进行进一步优化和调整。同时,实测结果还可以用于校准仿真模型,提高仿真的准确性。

四、总结与展望

高速电路设计是一个复杂而精细的过程,需要工程师具备深厚的专业知识和丰富的实践经验。本文介绍了高速电路设计的核心要素和技术要点,希望能为从事相关工作的工程师们提供有益的参考和借鉴。随着科技的不断发展,高速电路设计将面临更多的挑战和机遇。只有不断学习和创新,才能在这个日新月异的领域中保持领先地位。