射频PCB的设计与制造过程还包括使所有东西都变成50欧姆。假设第一次设计RF PCB布局,并且没有可用的合适工具来模拟3D设计,那么可以尝试的最佳替代方法是选择RF端口上特征阻抗为50欧姆的组件。

为什么是50欧姆?因为50欧姆是进行阻抗匹配的最佳值。这包括微带阻抗计算,以了解其电阻。此外,还可以适当调整走线宽度,以使承载RF信号的PCB上的走线阻抗变为50欧姆。可以使用在线走线阻抗计算器或微带阻抗计算器来计算走线宽度。使用CPWG(地上共面波导)结构在射频PCB上构建50Ω RF迹线。最后,实际上很容易找到组件(例如天线,滤波器,放大器等)。

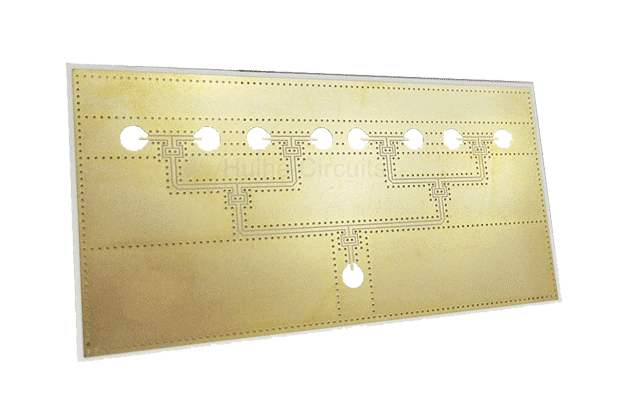

布置射频走线。射频PCB设计时,走线首先要考虑的优先事项,因为它是极端的高频信号传输结构。这就是为什么,如果将它们放在最后,或者在板子已经变得笨拙时尝试将它们放置,则会在走线布局方面做出妥协。最终可能会使您的设计失败。最后,请确保在信号走线周围留有足够的空间,以平滑弯曲并隔离RF信号。

隔离射频走线很重要。确保使射频走线与其他高速信号(例如,HDMI,以太网,USB差分对,晶体的时钟走线等)适当隔离。通常,它通过“通过缝合”来使用。例如,在RF走线周围缝上通孔,以防止其干扰射频PCB板上的其他组件。要记住,不适当的隔离不会使设计失效。但是,在大多数情况下,它将降低接收机性能和平均数据吞吐量。因此,对于过滤器或匹配网络的各个部分,请使用隔离的过孔。